DZ- Koddeswari M-CKD- EC 737

National Institute of Technology Hamirpur

Department of Electronics and Communication Engineering Letel.

## B.Tech ECE Dual Degree

End Semester Examination - Nov/Dec 2023

Course: VLSI TEST AND TESTABILITY

Course number: EC-737 Duration: 2:30PM-5:30PM

Date: 01/12/2023

Semester: VII

Answer all Questions

Maximum marks: 50

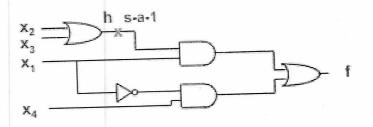

Find the test vector to determine the S-A-1 fault at node h in Fig.1 using truth table (5) method.

Fig.1

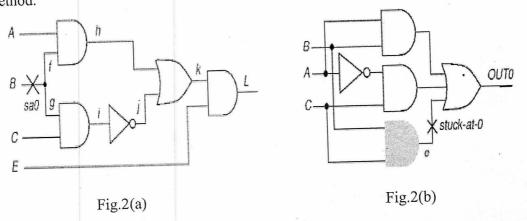

- a) Find the test set to determine the S-A-0 fault at node B in the Fig.2(a) using Boolean (5) 2 difference method.

- b) Find the test set to test S-A-0 fault at node e in Fig.2(b) using Boolean Difference method.

Explain the genetic algorithm for simulation based ATPG.

- (5)

- a) Explain fault equivalence of 2 input AND and OR gate for stuck at 0 and stuck at 1 (3) 4. fault at the output, respectively. (2)

- b) Define terms Controllability and Observability.

- Explain Logic BIST system and its classification with neat diagram.

(5)

- 6. a) Brief about controlling value and inversion value for a combinational circuit and discuss how the gate evaluation is carried out by input scanning.

- b) Illustrate the bridging fault model for "X dominates Y if X=1". (1)

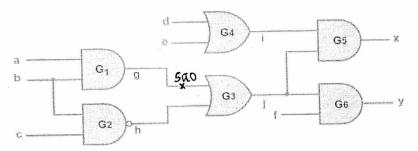

- 7. Demonstrate the application of the D algorithm by deriving a test for detecting (5) the g-s-a-0 fault in the circuit given in Fig. 3.

Fig.3 Circuit under test for D Algorithm

- a) Explain Logic BIST system and its classification with neat diagram.

b) What is meant by hazards? Mention its types and how they are detected.

(2)

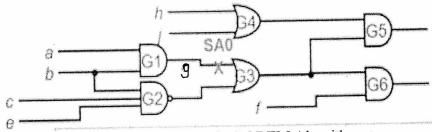

- 9. Illustrate the application of PODEM algorithm using the logical circuit shown in (5) Fig.4. Derive test vector for the circuit considering wire g with S-A-0 fault.

Fig.4 Circuit under test for PODEM Algorithm

- a) Construct a pseudo random sequence generator using the primitive polynomial (3) 1+x+x<sup>4</sup> with external XOR LFSR. Identify the proper seed value for the LFSR to get the maximal length sequence.

- b) Brief about Shorts and Opens in Wires.

(2)